En estos tres o cuatro meses he tenido el placer de ser alumno y docente de la Diplomatura de Desarrollo Seguro de Aplicaciones de la UNSTA.

La convocatoria

La organización me contactó para ver si podía dar una "charla magistral" de una hora y media de algún tema interesante y llamativo. Pensé un rato y ofrecí, en consonancia con lo que vengo haciendo últimamente, algo de seguridad de hardware. En la conversación fue creciendo y finalmente se convirtió en una materia de 9 horas.

|

| Evidencia en LinkedIn |

Todo un desafío, nunca había dictado algo así antes. Había conversado con la organización de los cursos del Laboratorio de Sistemas Embebidos de la Facultad de Ingeniería de la Universidad de Buenos Aires (CESE, CEIoT), donde soy docente de Ciberseguridad en IoT y, no sé si seguirá existiendo, Testing de Sistemas IoT, la posibilidad de organizar una materia optativa de esta misma naturaleza, pero medio que más que ofrecerlo lo estaba pidiendo. O mejor dicho, algún tipo de "colaboración", con algunas otras personas para armarlo y que mi rol sea más "seguridad pura" que de los aspectos más técnicos del hardware. Pero debido a que es un esfuerzo infernal, son cursos orientados a alumnos de posgrado, los docentes suelen estar extremadamente ocupados y en promedio son más responsables que yo, no se sentían capacitados y no prosperó.

En las diplomaturas la ventaja es que las condiciones de aceptación de alumnos es un tanto más relajada y la exigencia general también. Un indicador sencillo es que una diplomatura como ésta o como otra que he hecho de Seguridad Bancaria, tiene una carga de 100 horas, dos a cuatro clases por materia.

Los otros cursos tienen 15 materias de 8 clases cada una, son 24 horas cada materia, 360 horas en total. Incluso la carga semanal es un 50% mayor, dos contra tres días por semana. Cada materia suele tener unos ejercicios heavies y se espera que el trabajo práctico consuma unas 600 horas/persona, aunque no necesariamente sean todas tuyas, vale dirigir el trabajo de otras personas.

Respecto a la carga horaria del TP de esta diplomatura, calculo que si estuviste haciendo los ejercicios durante la cursada debe ser leve, pero si lo hubiera hecho completo yo solo me hubiera llevado hasta 40 horas.

Volviendo a mi participación como docente, me encontré con el siguiente FODA, un poco retrospectivo pues en ese momento aunque intuitivamente lo apliqué no lo llegué a concientizar:

Fortalezas

Experiencia en dar clases, experiencia en investigar seguridad de hardware aunque quizás de un modo un tanto esotérico, experiencia en ciberseguridad. Equipamiento de hardware apropiado.

Oportunidades

Poner a prueba el conocimiento que vengo juntando desde hace décadas. Identificar baches.

Debilidades

Conocimiento fragmentario e incompleto, desconocimiento de normas y electrónica en general. Falta de orden.

Amenazas

No llegar en tiempo y/o forma y pasar vergüenza ante los alumnos y/o la organización.

Preparativos

En las H4CK3D y en muchas charlas internas del trabajo ya había expuesto del tema de modo fragmentario y continué haciéndolo hasta antes e incluso después de las clases.

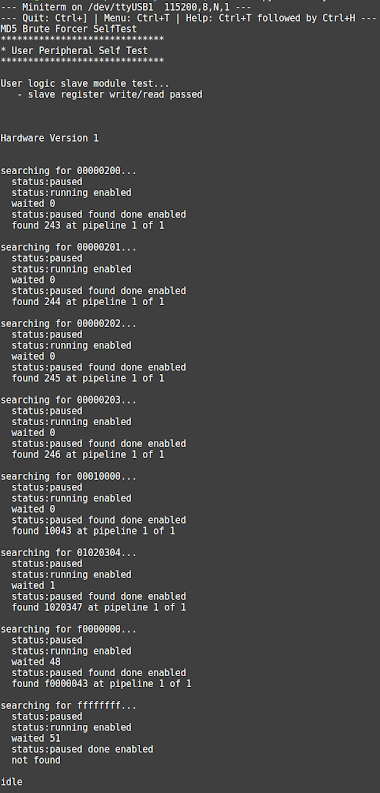

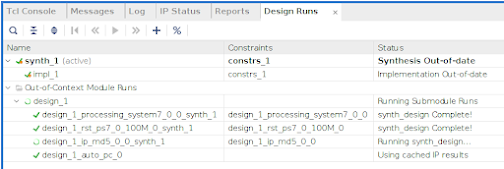

Tomé en simultáneo la materia Micro Arquitecturas y Soft Cores del CESE, que aunque no tenía relación directa, forma parte del conocimiento de base.

Resultados

Tuve muy poco feedback, sin sorpresas ("te falta un poco de orden"), no tuve la sensación de haber fallado en las dos primeras clases, quizás la tercera estuvo floja pero más por mis expectativas, no sé si se notó "para afuera". Me había propuesto mostrar una demo de Secure Boot con ESP32-S pero en parte por que no llegué a hacer las pruebas y en parte por que no le encontré que fuera realmente interesante, sólo lo expliqué en términos teóricos.

De algún modo no logré un "relato", el poder recorrer los temas de un modo hilvanado. En las charlas que doy pego saltos, que te obligan a prestar demasiada atención, imposible a lo largo de tres clases, te olvidaste. Las charlas son para gente que eligió ir específicamente (igual alguien se ha quejado), en las clases, aunque no falte a quien le interese mucho, hay que considerar que para la mayoría es una de diez materias y no precisamente la más útil o interesante.

Otra dificultad es que de todas las otras materias he recibido capacitación, tiene un poco del ¿Para qué hacés un curso de algo que ya mayormente sabés? que ya he mencionad en otro lado y para esta materia no, todo muy fragmentario y autodidacta.

Como alumno

En mi condición de docente tuve grandes facilidades económicas para ser alumno, con lo cual no fue una elección muy difícil, en todo caso si la experiencia era mala, salía con un título de utilidad moderada. La verdad es que no conocía a nadie, ni sus cualidades o defectos, es la primera edición, aposté y salió bien.

Siempre hay alguna clase que por el tema o el modo de quien la dicta es un poco más aburrida y otra más entretenida, pero no ocurrió ninguna vez que me arrepintiera. No hubieron clases malas y sí hubieron clases muy, muy buenas, lamentablemente no tomé nota, siempre confiando en que luego se puede acceder a las presentaciones y confiando de modo completamente injustificado en mi memoria.

Hubo una cierta falta de coordinación entre las materias, algunos temas

se vieron repetidos, no es tan terrible, es bueno el repaso. Pero

algunos temas como que se escaparon, igual nada grave.

Si se repite, si los tiempos me dan, si me dejan, probablemente asista como oyente, esta vez tomando notas.

Las clases quedan grabadas, pero la verdad es que no me gusta ver grabaciones.

El trabajo práctico

Para quienes no estamos programando todo el día y más web, fué bastante heavy. Además llegó un poco tarde y en mi caso coincidió con que como docente tenía que terminar de preparar las clases, como alumno de otra materia en otro lado tenía que terminar su trabajo práctico, un fondo de ojo que me dejó muerto justo el día de la entrega, log4shell me dejó agotado cada día de esa semana y la anterior, el día del asado del trabajo y que dí una charla de Chain of Trust y Secure Boot en el trabajo aprovechando parte del material que había usado para las clases.

Tampoco ayudó, en mi caso, un poco de actitud liebre y tortuga, liebre en mi caso. Ya que cuento con experiencia tanto en desarrollo como en seguridad, medio que aflojé un poco. Pude haber canibalizado un trabajo práctico a medio hacer del CEIoT pero me dá un poco de vergüenza y además necesitaba hacer un reajuste mental de varios días, hace meses que no toco programación web y node.

Estaba compuesto de varias partes, una relacionada a bases de datos y enmascaramiento, otra de obtener información de una virtual vulnerable, la tercera corregir una aplicación y la cuarta, más grande que las otra dos juntas, era hacer una API, agregarle autenticación y con tests de Postman mostrar su seguridad, todas cosas que sé hacer pero en este momento no estoy "sintonizado", mi cerebro está en FPGA.

Conclusión

Para decirlo del modo más corto posible, espero con ansia que se repita para que asistan las personas a las que invité en esta ocasión pero por haber sido con tan poco tiempo de aviso no pudieron asistir. Y por el lado docente, para tener la oportunidad de mejorar las clases. En términos de inversión, paga, quizás no como título pues es una Licenciatura, sujeto a interpretación, pero el resto está ok.

La profundidad y extensión de los temas fue correcta así como la calidad. Me hubiera gustado tener más feedback de mi materia.